碎碎念

很久没更了,小更怡情(doge

FPGA 菜鸟生活还是很顺利的(指顺利成为菜鸟),最近在忙老师的项目,遇到点小问题,所以随手记一下,另外博客的数据库出了点问题,这两天才想起来小修小补一下,不过不知道什么时候就又挂了💔

PS:太久不写了还是有点手生,感觉写出来的东西有点不尽人意,怎么说呢🤔,就是 CSDN 味很重。

希望多写点东西能早日恢复吧。

配置引脚控制一劳永逸

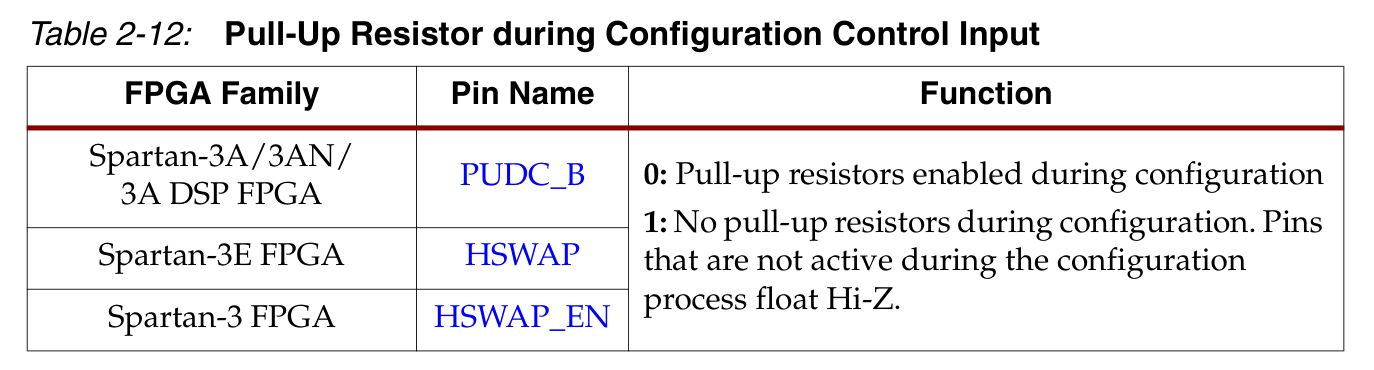

在烧录的过程中,通过控制配置引脚的电平来控制所有用户 IO 的电平,配置引脚在不同的系列中是不同的(Extended Spartan-3A 是 PUDC_B,Spartan-3E 是 HSWAP,Spartan-3、Virtex-II 和 Virtex-II Pro FPGA 是 HSWAP_EN,Virtex-4 和 Virtex-5 FPGA 是 HSWAPEN),当此引脚为高电平,每个用户 I/O 上的内部上拉电阻被禁用,同时,I/O 在配置过程中处于 high-Z 状态。反之当该引脚为低电平,上拉电阻网会启用,IO 在配置过程中被上拉为高电平。

以 Spartan 3 系列为例,手册中对于相关内容的描述如下:

上下拉电阻控制力大砖飞

在实际应用的层面,直接使用电阻上下拉其实是更容易想到的方法。

在不改动配置引脚的情况下,如果 IO 被配置为高阻态,上下拉自然没有任何问题;但是如果 IO 被配置为上拉,那么为了获取低电平我们需要的下拉电阻值其实是很难确定的。

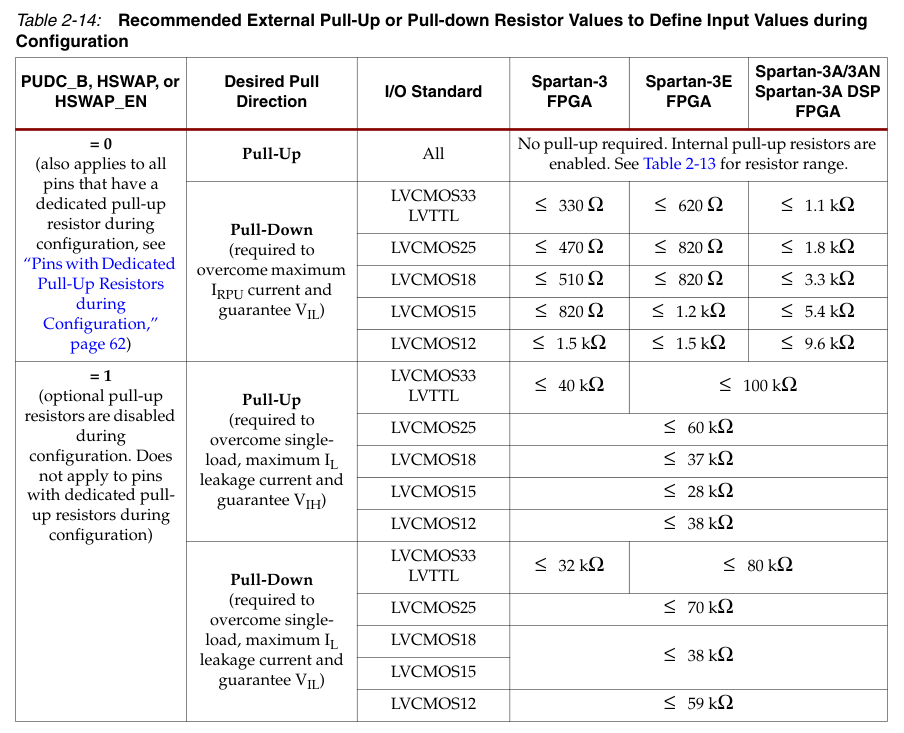

还是以 Spartan 3 系列为例,在手册中其实是充分考虑到了这个问题的,因此给出了临时改变 IO 电平所需要的下拉电阻推荐值。